# Datasheet

# BL5340

Version 2.1

# **Revision History**

| Version | Date        | Notes                                             | Contributor(s)  | Approver       |

|---------|-------------|---------------------------------------------------|-----------------|----------------|

| 1.0     | 19 Aug 2021 | Final updates for production release              | Raj Khatri      | Jonathan Kaye  |

| 1.1     | 14 Oct 2021 | Update Table 45 (removed unnecessary row)         | Raj Khatri      | Jonathan Kaye  |

| 1.2     | 23 Dec 2021 | Updated Mechanical Details                        | Dave Drogowski  | Andrew Chen    |

| 1.3     | 10 Jan 2022 | Updated Other Internal Clocks                     | Raj Khatri      | Dave Drogowski |

| 1.4     | 16 Aug 2023 | Updated Tape and Reel Package Information section | Robert Gosewehr | Dave Drogowski |

| 1.5     | 22 Apr 2024 | Fixed typo                                        | Dave Drogowski  | Joe Vattimo    |

| 1.6     | 1 Nov 2024  | Updated Bluetooth SIG Qualification               | Dave Drogowski  | Jonathan Kaye  |

| 2.0     | 23 Jan 2025 | Ezurio rebranding                                 | Sue White       | Dave Drogowski |

| 2.1     | 4 June 2025 | Updated Bluetooth SIG Qualification               | Dave Drogowski  | Jonathan Kaye  |

|         |             |                                                   |                 |                |

# Contents

| 1   | Overv    | riew and Key Features                                                                      | 6                                              |

|-----|----------|--------------------------------------------------------------------------------------------|------------------------------------------------|

|     | 1.1      | Features and Benefits                                                                      | 6                                              |

|     | 1.2      | Application Areas                                                                          | 6                                              |

| 2   | Spec     | fication                                                                                   | 7                                              |

|     | 2.1      | Specification Summary                                                                      | 7                                              |

| 3   | Hardy    | vare Specifications                                                                        | 12                                             |

|     | 3.1      | Block Diagram and Pin-out                                                                  | 12                                             |

|     | 3.2      | Pin Definitions                                                                            | 14                                             |

|     | 3.3      | Electrical Specifications                                                                  | 17                                             |

|     | 3.3.1    | Absolute Maximum Ratings                                                                   |                                                |

|     | 3.3.2    | Recommended Operating Parameters                                                           |                                                |

|     | 3.4      | Application Core and Network Core                                                          |                                                |

|     | 3.5      | Clocks                                                                                     | 21                                             |

|     | 3.5.1    | HFXO - 32MHz crystal oscillator and nRF53 internal load capacitor 13.5pF mandatory setting | 21                                             |

|     | 3.5.2    | LFCLK – Low Frequency clock source                                                         | 21                                             |

|     | 3.5.3    | Other Internal Clocks                                                                      |                                                |

|     | 3.6      | BL5340 Power Supply Options                                                                | 24                                             |

|     | 3.6.1    | Normal Voltage mode (option1) or High Voltage mode (option2)                               |                                                |

|     | 3.6.2    | VBUS pin and 4.7uF Mandatory Capacitor                                                     |                                                |

|     | 3.6.3    | VREQCTRL - Voltage request control (VREQCTRL ON for +3dB extra RF TX power)                |                                                |

|     | 3.6.4    | Low Power Modes                                                                            |                                                |

|     | 3.7      | Programmability                                                                            |                                                |

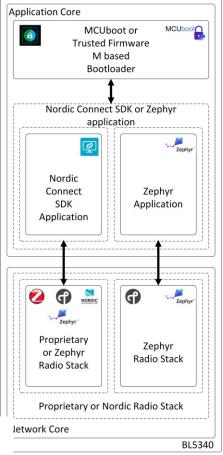

|     | 3.7.1    | BL5340 Firmware options                                                                    |                                                |

| 4   | Powe     | r Consumption                                                                              |                                                |

| 5   | Perip    | nerals                                                                                     |                                                |

|     | 5.1      | RADIO – 2.4GHz radio (RF)                                                                  |                                                |

|     | 5.2      | NFC Tag – Near field communication tag                                                     |                                                |

|     | 5.2.1    | Use Cases                                                                                  |                                                |

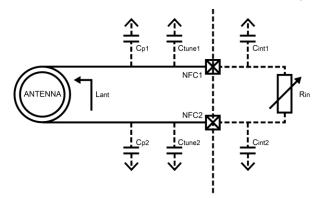

|     | 5.2.2    | NFC Antenna Coil Tuning Capacitors                                                         |                                                |

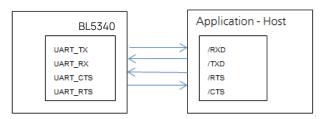

|     | 5.3      | UARTE - Universal asynchronous receiver/transmitter with Easy DMA                          |                                                |

|     | 5.4      | USB D - Universal Serial Bus device                                                        |                                                |

|     | 5.5      | SPI Master – Serial Peripheral Interface master                                            |                                                |

|     | 5.6      | SPI Slave – Serial Peripheral Interface slave                                              |                                                |

|     | 5.7      | QSPI – Quad Serial Peripheral interface                                                    |                                                |

|     | 5.8      | TWIM – I2C compatible 2-wire interface master                                              |                                                |

|     | 5.9      | TWIS – I2C compatible 2-wire interface master                                              |                                                |

|     | 5.10     | GPIO – General Purpose Input /Output                                                       |                                                |

|     | 5.11     | SAADC – Successive approximation analog-to-digital convertor                               |                                                |

| htt | ps://www | v.ezurio.com/ 3                                                                            | © Copyright 2025 Ezurio<br>All Rights Reserved |

|    | 5.12   | COMP - Comparator                                                                                      |    |

|----|--------|--------------------------------------------------------------------------------------------------------|----|

|    | 5.13   | LPCOMP – Low power comparator                                                                          |    |

|    | 5.14   | PWM - Pulse Width Modulation                                                                           |    |

|    | 5.15   | TIMER – Timer/counter                                                                                  |    |

|    | 5.16   | RTC – Real Timer Counter                                                                               | 40 |

|    | 5.17   | TEMP – Temperature sensor                                                                              | 40 |

|    | 5.18   | Security/Privacy                                                                                       | 40 |

|    | 5.19   | RNG – Random number generator                                                                          | 40 |

|    | 5.20   | I2S – Inter-IC sound interface                                                                         | 40 |

|    | 5.21   | PDM – Pulse Density Modulation interface and digital microphones                                       |    |

|    | 5.22   | QDEC – Quadrature decoder                                                                              |    |

|    | 5.23   | nRESET – pin reset                                                                                     |    |

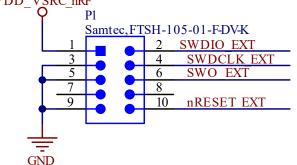

|    | 5.24   | SWD - Two-wire interface                                                                               |    |

|    | 5.25   | Peripheral Block Current Consumption                                                                   |    |

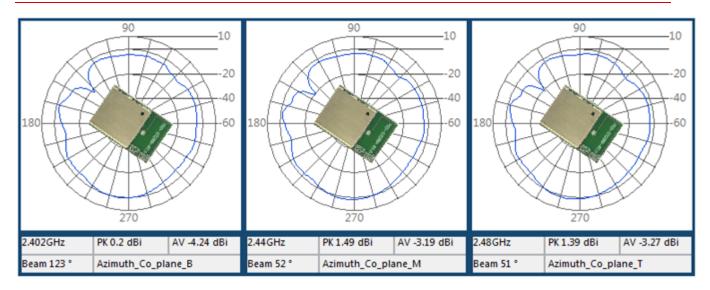

|    | 5.26   | 453-00052 On-Board PCB Trace Antenna Characteristics                                                   |    |

| 6  | Mand   | latory SW requirements related to hardware                                                             |    |

|    | 6.1    | 32MHz crystal internal load capacitor setting of 13.5pF                                                |    |

|    | 6.2    | CH26 (2480MHz) IEEE 802.15.4-2006 RF TX power                                                          |    |

| 7  | Hardv  | vare Integration Suggestions                                                                           |    |

|    | 7.1    | Circuit                                                                                                |    |

|    | 7.2    | PCB Layout on Host PCB - General                                                                       | 51 |

|    | 7.3    | PCB Layout on Host PCB for the 453-00052                                                               |    |

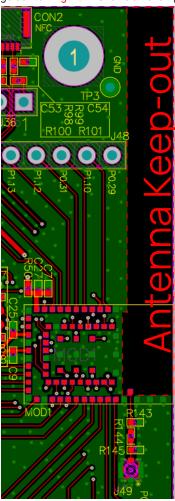

|    | 7.3.1  | Antenna Keep-out on Host PCB                                                                           |    |

|    | 7.3.2  | Antenna Keep-out and Proximity to Metal or Plastic                                                     | 53 |

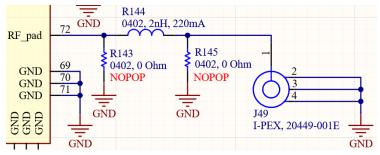

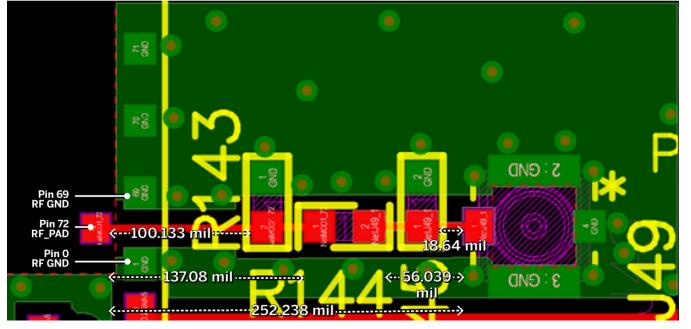

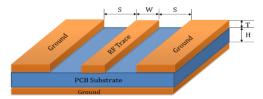

|    | 7.4    | 50-Ohms RF Trace and RF Match Series 2nH RF inductor on Host PCB for BL5340 RF pad variant (453-00053) | 53 |

|    | 7.5    | External Antenna Integration with the 453-00052                                                        |    |

| 8  | Mech   | anical Details                                                                                         | 57 |

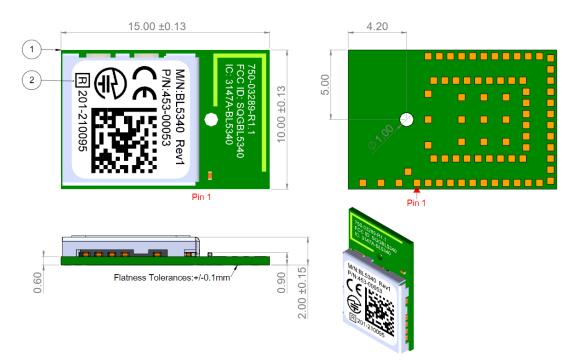

|    | 8.1    | BL5340 Mechanical Details                                                                              | 57 |

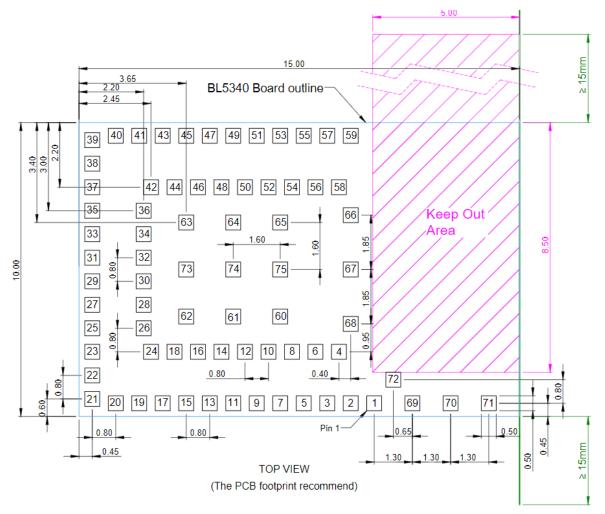

|    | 8.2    | Host PCB Land Pattern and Antenna Keep-out for the 453-00052                                           |    |

| 9  | Applic | cation Note for Surface Mount Modules                                                                  | 59 |

|    | 9.1    | Introduction                                                                                           | 59 |

|    | 9.2    | Shipping                                                                                               | 59 |

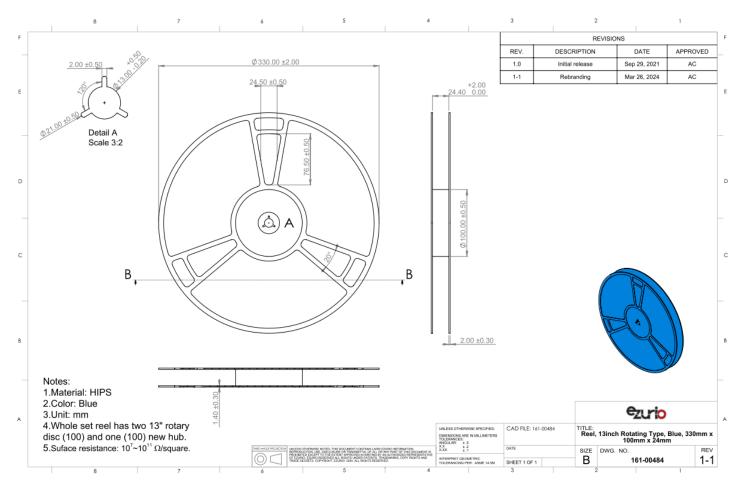

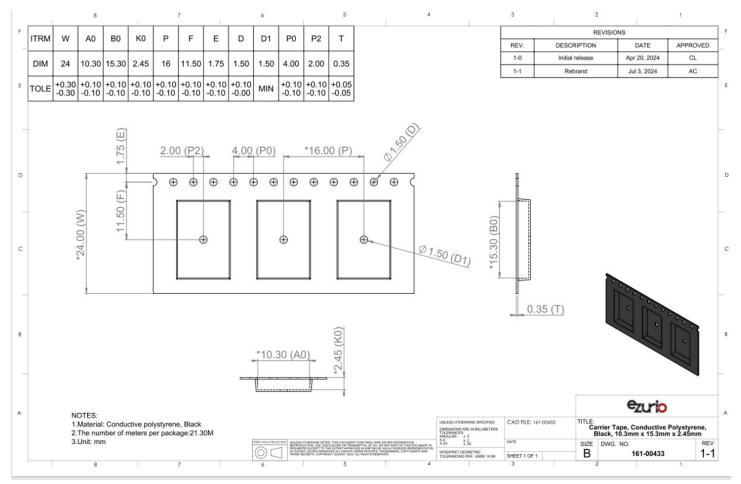

|    | 9.2.1  | Tape and Reel Package Information                                                                      | 59 |

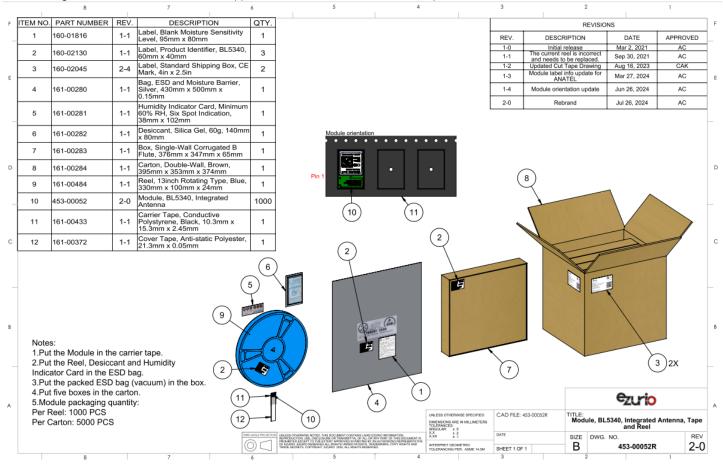

|    | 9.2.2  | Carton Contents and Packaging Process                                                                  | 61 |

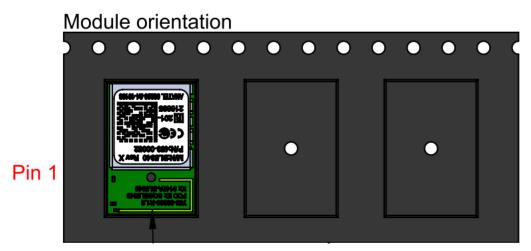

|    | 9.2.3  | Module Orientation in Cavity                                                                           | 61 |

|    | 9.2.4  | Labeling                                                                                               | 62 |

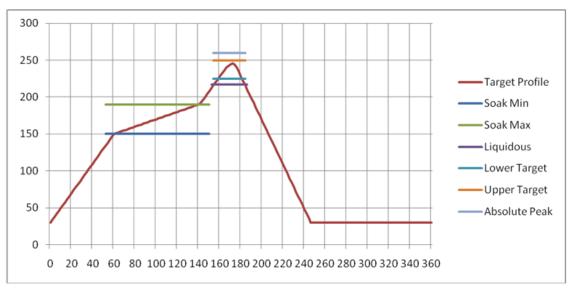

|    | 9.3    | Reflow Parameters                                                                                      | 62 |

| 10 | Regul  | latory                                                                                                 | 65 |

| 11 | Order  | ing Information                                                                                        | 65 |

|    |        |                                                                                                        |    |

# ezurio

| 12 | Blueto | ooth SIG Qualification                                                                                 | .66  |

|----|--------|--------------------------------------------------------------------------------------------------------|------|

| 1: | 2.1    | Overview                                                                                               | .66  |

| 1: | 2.2    | Scope                                                                                                  | .66  |

| 1: | 2.3    | Qualification Steps When Referencing multiple existing designs, (unmodified) – Option 2a in the QPRDv3 | .66  |

| 1: | 2.4    | Example Design Combinations                                                                            | .68  |

| 1: | 2.5    | Qualify More Products                                                                                  | .68  |

| 13 | Reliab | pility Tests                                                                                           | .69  |

| 14 | Additi | ional Information                                                                                      | . 70 |

# 1 Overview and Key Features

The BL5340 series of robust, tiny modules feature the Nordic nRF5340 SoC. It directly targets the highest performance with the lowest power budget, with additional variants featuring integrated Nordic nRF21540 PA/LNA for higher TX Power applications. Featuring Bluetooth 5.2 including Isochronous Channels and LE Audio, the BL5340 supports next generation Bluetooth audio for stereo streaming and broadcast audio.

The dual core Arm<sup>®</sup> Cortex M33 microcontrollers enable you to run a low power core focused purely on wireless connectivity, with a second higher performance core targeted for the end application itself. This further extends the multi-protocol capabilities of the product: Bluetooth LE, 802.15.4 (Thread / Zigbee) and NFC. It's further enhanced with an ARM CryptoCell-312 including trusted execution, root-of-trust and secure key storage security features.

The BL5340 series brings out all nRF5340 hardware features and capabilities including USB access, up to +3 dBm transmit power, from 1.7V to 5.5V supply considerations, and a true industrial operating range of -40 to 105°C. Complete regulatory certifications enable faster time to market and reduced development risk completes Ezurio's simplification of your next multi-protocol wireless design!

Note: BL5340 hardware provides all functionality of the nRF5340 chipset used in the module design. This is a hardware datasheet only – it does not cover the software aspects of the BL5340. This is to acknowledge that information in this datasheet is referenced from the nRF5340 datasheet – consult for details: https://infocenter.nordicsemi.com/topic/ps\_nrf5340/keyfeatures\_html5.html?cp=3\_0\_0

# 1.1 Features and Benefits

- Based on Nordic Semiconductor nRF5340 silicon

- Bluetooth v5.2 Single mode

- NFC

- IEEE 802.15.4-2006 (Thread or Zigbee) radio support

- External or internal antennas

- Programmable Tx power +3 dBm to -20 dBm, -40 dBm

- Rx sensitivity -98 dBm (1 Mbps), 104 dBm (125 kbps)

- Ultra-low power consumption

- Tx 5.1 mA peak (at +3 dBm, DCDC on) (See Note 1 in the *Power Consumption* section)

- Rx: 2.7 mA peak (DCDC on) (See Note 1 in the *Power Consumption* section)

# 1.2 Application Areas

- Medical devices

- IoT Sensors

- Access Control

- System ON Idle 1.3 uA typical

- System OFF 0.9 uA (See Note 4 in the *Power Consumption* section)

- UART, GPIO, ADC, PWM, timers, I2C, QSPI, SPI, I2S, PDM, and USB interfaces

- FCC, CE, ISED, RCM, MIC and UKCA certified

- Full Bluetooth Declaration ID

- Other regulatory certifications on request

- No external components required

- Industrial temperature range (-40° C to +105° C)

- Health & Wellness devices

- Location awareness

- Factory automation

# 2 Specification

# 2.1 Specification Summary

| Categories/Feature                                                                                             | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |                                                        |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Wireless Specification                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                     |                                                        |

| Bluetooth®                                                                                                     | <ul> <li>Bluetooth 5.2 - Single mode</li> <li>Isochronous Channels (LE Audio) - BT 5.2</li> <li>EATT - BT5.2</li> <li>LE Power Control - BT 5.2</li> <li>4x Range (CODED PHY support) - BT 5.1</li> <li>2x Speed (2M PHY support) - BT 5.1</li> <li>LE Advertising Extension - BT 5.1</li> <li>Diffie-Hellman based pairing (LE Secure Connections) - BT 4.2</li> <li>Data Packet Length Extension - BT 4.2</li> <li>Link Layer Privacy (LE Privacy 1.2) - BT 4.2</li> <li>Concurrent master, slave</li> <li>BLE Mesh capabilities</li> <li>Bluetooth direction finding</li> </ul> |                                                                                                                                     |                                                        |

| IEEE 802.15.4-2006 PHY                                                                                         | <ul> <li>Bidetoorn direction miding</li> <li>2405–2480 MHz IEEE 802.15.5-2006 radio transceiver, implementing IEEE 802.15.5-2006 compliant</li> <li>250kbps,2450MHz, O-QPSK PHY</li> <li>Channels 11-26. Channel 11 2405MHz and CH26 2480MHz.</li> <li>Clear channel assessment (CCA)</li> <li>Energy detection (ED) scan</li> <li>CRC generation</li> </ul>                                                                                                                                                                                                                       |                                                                                                                                     |                                                        |

| Nordic proprietary 1Mbps and 2Mbps<br>modes radio ( <i>not currently certified</i><br><i>by Ezurio</i> )       | <ul> <li>2402-2480 MHz Nordic proprietary 1Mbps and 2Mbps modes radio transceiver</li> <li>1Mbps nRF proprietary mode (ideal transmitter)</li> <li>2Mbps nRF proprietary mode (ideal transmitter)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     |                                                        |

| Frequency                                                                                                      | 2.402 - 2.480 GHz for BLE (CH0 to CH39)<br>2.405 - 2.480 GHz for IEEE 802.15.4-2006 PHY (CH11 to CH26)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     |                                                        |

| Raw Data Rates                                                                                                 | 2 Mbps BLE<br>125 kbps BL<br>500 kbps B<br>250 kbps IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (over-the-air)<br>: (over-the-air)<br>.E (over-the-air)<br>LE (over-the-air)<br>EE 802.15.4 802.15.4-200<br>prietary 1Mbps and 2Mbp |                                                        |

| Maximum Transmit Power Setting<br><i>(See <mark>Note 1</mark> in the Module</i><br><i>Specification Notes)</i> | +3 dBm<br>+3 dBm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Conducted 453-00052 (Integrated antenna)<br>Conducted 453-00053 (External antenna)                                                  |                                                        |

| Minimum Transmit Power Setting                                                                                 | -40 dBm, -20 dBm (in 4 dB steps)<br>-16 dBm, -12 dBm, - 8 dBm, - 7 dBm, -6 dBm, -5 dBm, -4 dBm, -3 dBm, -2 dBm, -1 dBm, 0dBr<br>+1dBm, +2dBm                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     | 6 dBm, -5 dBm, -4 dBm, -3 dBm, -2 dBm, -1 dBm, 0dBm,   |

| Receive Sensitivity (≤37byte packet<br>for BLE)                                                                | BLE 2 Mbps-92 dBm typicalBLE 125 kbps-104 dBm typicalBLE 500 kbps-99 dBm typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                     | -92 dBm typical<br>-104 dBm typical<br>-99 dBm typical |

|                                                                                                                | IEEE 802.15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-2006 250kbps                                                                                                                      | -101 dBm typical                                       |

| Categories/Feature                                                            | Implementat   | Implementation                              |  |  |  |

|-------------------------------------------------------------------------------|---------------|---------------------------------------------|--|--|--|

| Link Budget (conducted)                                                       | 101 dB        | @ BLE 1 Mbps                                |  |  |  |

|                                                                               | 107 dB        | @ BLE 125 kbps                              |  |  |  |

| NFC                                                                           |               |                                             |  |  |  |

| NFC-A Listen mode compliant<br>13.5<br>Date<br>NFC<br>Modes or<br>Disa<br>Sen |               | e 106 kbps<br>e2 and Type 4 emulation       |  |  |  |

|                                                                               | Use Cases:    |                                             |  |  |  |

|                                                                               |               | o-Pair with NFC<br>bled Out-of-Band Pairing |  |  |  |

| System Wake-On-Field function                                                 | Proximity Det | ection                                      |  |  |  |

| Host Interfaces and Peripherals | Applications Core (High Performance)     | Network Core (ultra-low power) |  |

|---------------------------------|------------------------------------------|--------------------------------|--|

| Total                           | 48 x multifunction I/O lines             |                                |  |

| Two co-processors               | Arm Cortex-M33 with DSP, FPU, TrustZone  | Arm Cortex-M33                 |  |

|                                 | support.                                 | 256kB Flash                    |  |

|                                 | 1024kB Flash                             | 64kB RAM                       |  |

|                                 | 512kB RAM                                | 2kB instruction cache          |  |

|                                 | 8kB 2-way associative cache              | 64MHz clock                    |  |

|                                 | 128 and 64MHz clock                      |                                |  |

|                                 | Uses voltage and clock frequency scaling |                                |  |

| UART          | 4 x UART (with CTS, RTS)                | 1 x UART (with CTS, RTS)                       |  |  |

|---------------|-----------------------------------------|------------------------------------------------|--|--|

| USB           | 1 x USB 2.0 FS (Full Speed, 12Mbps)     | -                                              |  |  |

| GPIO          | GPIO Up to 48                           |                                                |  |  |

|               | 32 x GPIOs on P0.00 to P0.31            |                                                |  |  |

|               | 15 :                                    | x GPIOs on P1.00 to P1.15                      |  |  |

|               |                                         | With configurable                              |  |  |

|               |                                         | I/O direction,                                 |  |  |

|               | O/P drive strengt                       | h (standard 0.5 mA or high 3mA/5 mA),          |  |  |

|               |                                         | Pull-up /pull-down                             |  |  |

|               | lr                                      | nput buffer disconnect                         |  |  |

| ADC (200kbps) | Eight 8/10/12-bit channels on AIN0-/    | AIN7 or -                                      |  |  |

|               | VDD or VDDH/5                           |                                                |  |  |

|               | 14-bit resolution with oversampling     | AINO-                                          |  |  |

|               | AIN7                                    |                                                |  |  |

|               | Configurable reference internal refe    | erence                                         |  |  |

|               | 0.6V or external reference VDD/4        |                                                |  |  |

|               | Configurable pre-scaling of 4, 2, 1, 1/ | Configurable pre-scaling of 4, 2, 1, 1/2, 1/3, |  |  |

|               | 1/4, 1/5 1/6                            |                                                |  |  |

|               | Configurable acquisition time 3uS, 5    | 5uS,                                           |  |  |

|               | 10uS (default), 15uS, 20uS, 40uS.       |                                                |  |  |

|               | One-shot mode or Burst mode             |                                                |  |  |

| lost Interfaces and Peripherals | Applications Core (High Performance)                                                                                                                     | Network Core (ultra-low power)                                                                                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                 | Scan mode for multiple channels                                                                                                                          |                                                                                                                   |

|                                 | Single ended or Differential or not connected                                                                                                            |                                                                                                                   |

| COMP                            | 1 x COMP (comparator)                                                                                                                                    | -                                                                                                                 |

| LPCOMP                          | 1 x LPCOMP (low power comparator)                                                                                                                        | -                                                                                                                 |

| High-Speed SPI                  | 1 x High-speed SPI (32Mbps, SPIM4) master<br>or slave with Easy DMA<br>on dedicated pins                                                                 | -                                                                                                                 |

| SPI                             | 4 x SPI (upto 16Mbps) master or slave with<br>Easy DMA                                                                                                   | 1 x SPI master or slave with Easy DMA<br>Slave is upto 8Mbps                                                      |

|                                 | Slave is upto 8Mbps                                                                                                                                      |                                                                                                                   |

| High-Speed TWI (I2C)            | 1 x High-speed TWI (1Mbps) master or slave with Easy DMA                                                                                                 | 1 x High-speed TWI (1Mbps) master or slave<br>with Easy DMA                                                       |

|                                 | on dedicated pins                                                                                                                                        | on dedicated pins                                                                                                 |

| TWI (I2C)                       | 3 x TWI (upto 400kps, 200kbps, 100kbps)<br>master or slave with Easy DMA                                                                                 | 1 x TWI (upto 400kps, 200kbps, 100kbps))<br>master or slave with Easy DMA                                         |

| QSPI                            | 1 x QSPI interface (6 to 96MHz configurable<br>clock frequency) for communicating with<br>external flash memory.<br>XIP (Execution in Place) capability. | -                                                                                                                 |

| PWM                             | 4 x PWM (pulse width modulation) units with Easy DMA                                                                                                     | -                                                                                                                 |

| QDEC                            | 2 x QDEC (Quadrature decoder)                                                                                                                            | -                                                                                                                 |

| I2S                             | 1 x I2S (Inter-IC sound interface)                                                                                                                       | -                                                                                                                 |

| PDM                             | 1 x PDM (Pulse code modulation interface)<br>for digital microphones                                                                                     | -                                                                                                                 |

| TIMER                           | 3 x Timer (32bit)                                                                                                                                        | 3 x Timer (32bit)                                                                                                 |

| RTC                             | 2 x RTC (24bit)                                                                                                                                          | 2×RTC                                                                                                             |

| WDT                             | 2 x WDT (Watchdog timer)                                                                                                                                 | 2 x WDT (Watchdog timer)                                                                                          |

| EGU                             | 6 x EGU (Event generator unit)                                                                                                                           | 1 x EGU (Event generator unit)                                                                                    |

| RNG                             | -                                                                                                                                                        | 1 x RNG (random number generator)                                                                                 |

| TEMP                            | -                                                                                                                                                        | 1 x Temperature sensor<br>Temperature range equal to operating<br>temperature range                               |

| ECB                             | -                                                                                                                                                        | 1 x ECB (AES electronic codebook mode encryption)                                                                 |

| AAR                             | -                                                                                                                                                        | 1 x AAR (Accelerated address resolver)                                                                            |

| ССМ                             | -                                                                                                                                                        | 1 x CCM (AES CCM mode encryption)                                                                                 |

| RSSI                            | -                                                                                                                                                        | 1 x RSSI (Received Signal Strength<br>Detector),<br>1dB resolution.<br>±2 dB accuracy (valid over -90 to -20 dBm) |

| External optional 32.768 kHz crystal     | Not needed for normal radio operation.                                                                                                                                    |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Optionally, connect +/-20ppm accuracy crystal for more accurate protocol timing. Fit associated load capacitor for crystal or use nRF53 internal load capacitor, which is |

|                                          | configurable as either 6pF, 7pF or 9pF on pins XL1, XL2.                                                                                                                  |

| Programmability                          |                                                                                                                                                                           |

| Zephyr RTOS                              | Via SWD (JTAG) 2 wire interface                                                                                                                                           |

| Nordic nRFConnect                        | Via SWD (JTAG) 2 wire interface                                                                                                                                           |

| Supply Voltage                           |                                                                                                                                                                           |

| VDD                                      | Normal voltage mode VDD 1.7- 3.6 V – Internal DCDC converter or LDO                                                                                                       |

|                                          | OR                                                                                                                                                                        |

| VDD_HV                                   | High voltage mode VDD_HV 2.5V-5.5V Internal DCDC converter or LDO                                                                                                         |

| Power Consumption                        |                                                                                                                                                                           |

| Active Modes Peak Current (for           | 5.1 mA peak Tx (with DCDC)                                                                                                                                                |

| maximum Tx power +3 dBm)<br>- Radio only |                                                                                                                                                                           |

| Active Modes Peak Current (for Tx        | 2.6 mA peak Tx (with DCDC)                                                                                                                                                |

| power -40 dBm) – Radio only              |                                                                                                                                                                           |

| Active Modes Average Current             | Depends on many factors, see section Power Consumption                                                                                                                    |

| Ultra-low Power Modes                    | System ON Idle 1.3 uA (wake on any event)                                                                                                                                 |

|                                          | System OFF 0.9 uA (wake on reset)                                                                                                                                         |

| Antenna Options                          |                                                                                                                                                                           |

| Internal                                 | Printed PCB monopole antenna – on-board (453-00052 variant)                                                                                                               |

| External                                 | Dipole antenna (with IPEX MHF4 connector)                                                                                                                                 |

|                                          | Dipole PCB antenna (with IPEX MHF4 connector)                                                                                                                             |

|                                          | Connection via <i>off module</i> IPEX MH4 – <b>453-00053 variant (RF trace pin)</b>                                                                                       |

|                                          | See the <b>Regulatory</b> section and <i>Regulatory Information Guide</i> for FCC, ISED, MIC, RCM, UKCA and CE.                                                           |

|                                          | The certified list of external antennas is listed in External Antenna Integration with the 453                                                                            |

|                                          | 00052 section.                                                                                                                                                            |

| Physical                                 |                                                                                                                                                                           |

| Dimensions                               | 15.0 mm x 10 mm x 2.0 mm                                                                                                                                                  |

|                                          | Pad Pitch – 0.8 mm                                                                                                                                                        |

|                                          | Pad Type – Three rows of pads (LGA - Land Grid Array).                                                                                                                    |

| Weight                                   | <1gram                                                                                                                                                                    |

| Environmental                            |                                                                                                                                                                           |

| Operating                                | -40 °C to +105 °C                                                                                                                                                         |

| Storage                                  | -40 °C to +105 °C                                                                                                                                                         |

| Miscellaneous                            |                                                                                                                                                                           |

| Lead Free                                | Lead-free and RoHS compliant                                                                                                                                              |

| Warranty                                 | One-Year Warranty                                                                                                                                                         |

| Development Tools                        |                                                                                                                                                                           |

| Development Kit                          | Development kit per module SKU (453-00052-K1 and 453-00053-K1 respectively)                                                                                               |

| ·                                        |                                                                                                                                                                           |

# Optional (External to the BL5340 module)

| Bluetooth®               | Full Bluetooth SIG Declaration ID |

|--------------------------|-----------------------------------|

| FCC/ISED/CE/MIC/RCM/UKCA | All BL5340 Series                 |

## Module Specification Notes:

Note 1 MANDATORY. When used in IEEE 802.15.4-2006 PHY mode, channel 26 (2480MHz), the BL5340 RF TX power must be limited by customer to -8 dBm setting (which produces -5dBm with VREQCTRL ON) maximum RF transmit power to pass FCC/IC Band Edge emissions limit. All other 802.15.4 channels (11-25) may be used up to the maximum 0dBm (which produces +3 dBm with VREQCTRL ON) RF TX output power.

#### Note 2 VRE

VREQCTRL must be set ON to produce extra +3dB of RF TX power at each nRF5340 RF TX power setting.

| nRF5340 RF TX power setting | Register VREQCTRL OFF<br>Actual nRF5340 RF TX power | Register VREQCTRL ON (to add<br>extra +3dB)<br>Actual nRF5340 RF TX power |

|-----------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|

| 0 dBm                       | 0 dBm                                               | +3 dBm (= 0 dBm +3 dB)                                                    |

| -1 dBm                      | -1 dBm                                              | +2 dBm (= -1 dBm +3 dB)                                                   |

| -2 dBm                      | -2 dBm                                              | +1 dBm (= -2 dBm +3 dB)                                                   |

| -3 dBm                      | -3 dBm                                              | 0 dBm (= -3 dBm +3 dB)                                                    |

| -4 dBm                      | -4 dBm                                              | -1 dBm (= -4 dBm +3 dB)                                                   |

| -5 dBm                      | -5 dBm                                              | -2 dBm (= -5 dBm +3 dB)                                                   |

| -6 dBm                      | -6 dBm                                              | -3 dBm (= -6 dBm +3 dB)                                                   |

| -7 dBm                      | -7 dBm                                              | -4 dBm (= -7 dBm +3 dB)                                                   |

| -8 dBm                      | -8 dBm                                              | -5 dBm (= -8 dBm +3 dB)                                                   |

| -12 dBm                     | -12 dBm                                             | -9 dBm (= -12 dBm +3 dB)                                                  |

| -16 dBm                     | -16 dBm                                             | -13 dBm (= -16 dBm +3 dB)                                                 |

| -20 dBm                     | -20 dBm                                             | -17 dBm (= -20 dBm +3 dB)                                                 |

| -40 dBm                     | -40 dBm                                             | -37 dBm (= -40 dBm +3 dB)                                                 |

# 3 Hardware Specifications

# 3.1 Block Diagram and Pin-out

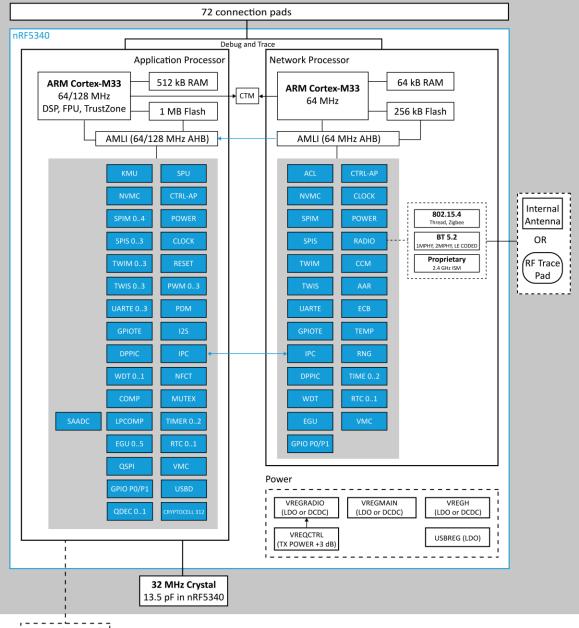

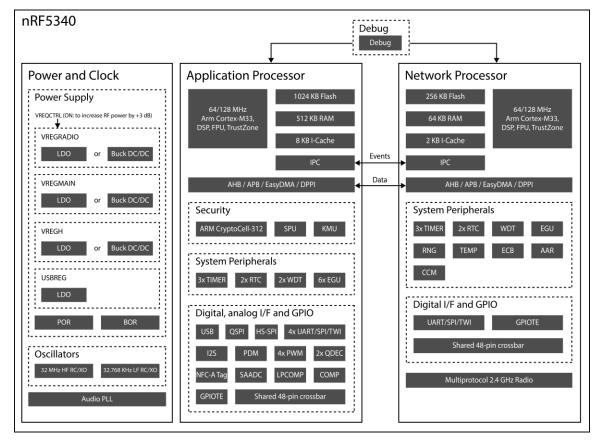

Optional External

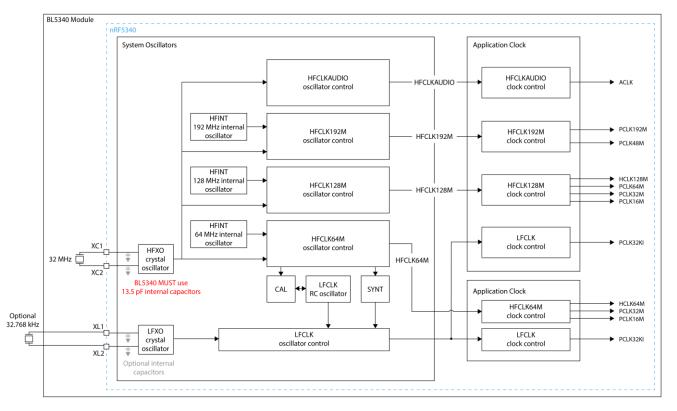

Figure 1: BL5340 HW block diagram

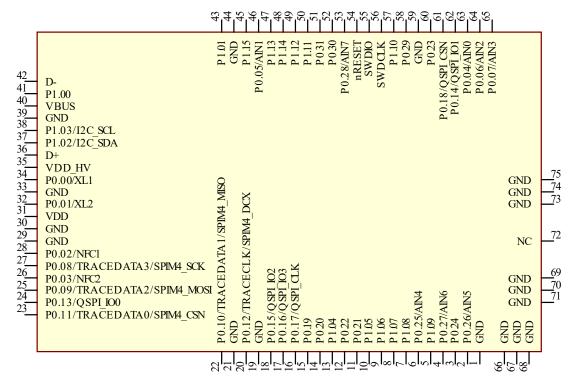

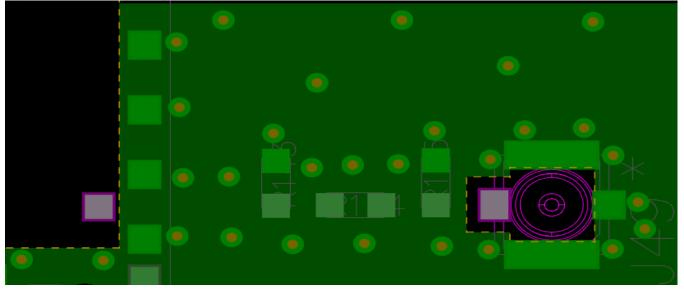

Figure 2: Top view - Schematic symbol for 453-00052 BL5340 Multi-Core/Protocol -Bluetooth +802.15.4+NFC Module (Nordic nRF5340) -Integrated Antenna

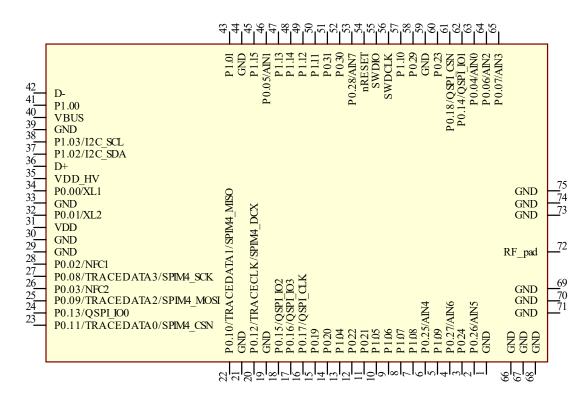

Figure 3: Top view - Schematic symbol for 453-00053 BL5340 Multi-Core/Protocol -Bluetooth +802.15.4+NFC Module (Nordic nRF5340) - Trace pin

# 3.2 Pin Definitions

# Table 1: Pin definitions

| Pin #    | Pin Name             | nRF5340<br>QFN Pin                      | nRF5340 QFN Name     | Comment                                                   |

|----------|----------------------|-----------------------------------------|----------------------|-----------------------------------------------------------|

| 1        | GND                  | -                                       | VSS                  | -                                                         |

| 2        | P0.26 / AIN5         | AL29                                    | P0.26 / AIN5         | Dedicated pin for ADC                                     |

| 2        | F 0.20 / AINS        | ALZJ                                    | F 0.207 AINS         | Ezurio Devkit: Ethernet chip SPI_MISO                     |

| 3        | P0.24                | AL27                                    | P0.24                | Ezurio Devkit:                                            |

| <u> </u> | 10.21                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1 0.2 1              | INT2_ACC interrupt from 3-axis accelerometer chip         |

| 4        | P0.27 / AIN6         | AK30                                    | P0.27 / AIN6         | Dedicated pin for ADC                                     |

|          |                      |                                         |                      | Ezurio Devkit: Ethernet chip SPI_MOSI                     |

| 5        | P1.09                | AK26                                    | P1.09                | Ezurio Devkit: UART1_CTS                                  |

| 6        | P0.25 / AIN4         | AK28                                    | P0.25 / AIN4         | Dedicated pin for ADC                                     |

| _        |                      |                                         |                      | Ezurio Devkit: Ethernet chip SPI_CS                       |

| 7        | P1.08                | AL23                                    | P1.08                | Ezurio Devkit: UART1_TX                                   |

| 8        | P1.07                | AK24                                    | P1.07                | Ezurio Devkit: UART1_RTS                                  |

| 9        | P1.06                | AL21                                    | P1.06                | Ezurio Devkit:                                            |

|          |                      |                                         |                      | Interrupt from Port Expander chip PE_INT                  |

| 10       | P1.05                | AK22                                    | P1.05                | See Note 6                                                |

| 11       | P0.21                | AL15                                    | P0.21                | Ezurio Devkit: UARTO_CTS                                  |

| 12       | P0.22                | AK18                                    | P0.22                | Ezurio Devkit: UARTO_RX                                   |

| 13       | P1.04                | AL19                                    | P1.04                | See Note 6                                                |

| 14       | P0.20                | AK16                                    | P0.20                | Ezurio Devkit: UARTO_TX                                   |

| 15       | P0.19                | AL13                                    | P0.19                | Ezurio Devkit: UARTO_RTS                                  |

| 16       | P0.17 / QSPI_CLK     | AK12                                    | P0.17 / QSPI_CLK     | Dedicated pin for QSPI                                    |

|          |                      |                                         |                      | Ezurio Devkit: QSPI flash chip                            |

| 17       | P0.16 / QSPI_103     | AL9                                     | P0.16 / QSPI_IO3     | Dedicated pin for QSPI                                    |

|          |                      |                                         |                      | Ezurio Devkit: QSPI flash chip                            |

| 18       | P0.15 / QSPI_IO2     | AK10                                    | P0.15 / QSPI_IO2     | Dedicated pin for QSPI<br>Ezurio Devkit: QSPI flash chip  |

| 19       | GND                  |                                         | VSS                  | Ezuno Devkit. Qort hash chip                              |

| 19       | GND                  | -                                       | V33                  | -<br>Dedicated pin for High-speed SPI (SPIM4, 32Mbps) and |

| 20       | P0.12 / TRACECLK /   | AK6                                     | P0.12 / TRACECLK /   | Trace                                                     |

| 20       | SPIM4_DCX            | ARO                                     | SPIM4_DCX            | Ezurio Devkit: LCD assembly SPIM4_DCX                     |

| 21       | GND                  | -                                       | VSS                  |                                                           |

| 21       | OND                  |                                         | 100                  | Dedicated pin for High-speed SPI (SPIM4, 32Mbps) and      |

| 22       | P0.10 / TRACEDATA1 / | AK2                                     | P0.10 / TRACEDATA1 / | Trace                                                     |

|          | SPIM4_MISO           | 7.11.2                                  | SPIM4_MISO           | Ezurio Devkit: LCD assembly SPIM4_SPI_MISO                |

|          |                      |                                         |                      | Dedicated pin for High-speed SPI (SPIM4, 32Mbps) and      |

|          | P0.11 / TRACEDATAO / |                                         | P0.11 / TRACEDATA0 / | Trace.                                                    |

| 23       | SPIM4_CSN            | AK4                                     | SPIM4_CSN            | SWO also comes out on P0.11                               |

|          |                      |                                         |                      | Ezurio Devkit: LCD assembly SPIM4_CS                      |

| <i></i>  |                      |                                         | D0 47 ( 000)         | Dedicated pin for QSPI                                    |

| 24       | P0.13 / QSPI_IO0     | AL5                                     | P0.13 / QSPI_IO0     | Ezurio Devkit: QSPI flash chip                            |

|          |                      |                                         |                      | Dedicated pin for High-speed SPI (SPIM4, 32Mbps) and      |

| 25       | P0.09 / TRACEDATA2 / | AJ1                                     | P0.09 / TRACEDATA2 / | Trace                                                     |

|          | SPIM4_MOSI           |                                         | SPIM4_MOSI           | Ezurio Devkit: LCD assembly SPIM4_MOSI                    |

|          |                      |                                         |                      | Dedicated pin for NFC                                     |

| 26       | P0.03 / NFC2         | AA1                                     | P0.03 / NFC2         | Ezurio Devkit: NFC Coil flexi-PCB NFC antenna plug into   |

|          |                      |                                         |                      | CON2                                                      |

|          |                      |                                         |                      | Dedicated pin for High-speed SPI (SPIM4, 32Mbps) and      |

| 27       | P0.08 / TRACEDATA3 / | AH2                                     | P0.08 / TRACEDATA3 / | Trace                                                     |

|          | SPIM4_SCK            |                                         | SPIM4_SCK            | Ezurio Devkit: LCD assembly SPIM4_SCL                     |

| Pin # | Pin Name        | nRF5340<br>QFN Pin | nRF5340 QFN Name | Comment                                                                                                                                                                                                                           |

|-------|-----------------|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28    | P0.02 / NFC1    | W1                 | P0.02 / NFC1     | Dedicated pin for NFC<br>Ezurio Devkit: NFC Coil flexi-PCB NFC antenna plug into<br>CON2                                                                                                                                          |

| 29    | GND             | -                  | VSS              | -                                                                                                                                                                                                                                 |

| 30    | GND             | -                  | VSS              | -                                                                                                                                                                                                                                 |

| 31    | VDD             | A19, B8, L1        | VDD              | 1.7V to 3.6V                                                                                                                                                                                                                      |

| 51    | 000             | A19, D0, L1        | VDD              | See 3.6 BL5340 Power Supply Options                                                                                                                                                                                               |

| 32    | P0.01 / XL2     | R1                 | P0.01 / XL2      | Dedicated pin for NFC<br>Ezurio Devkit: Optional 32.768kHz crystal pad XL2 and<br>associated 7pF load capacitor inside nRF5340 chipset.                                                                                           |

| 33    | GND             | -                  | VSS              |                                                                                                                                                                                                                                   |

| 34    | P0.00 / XL1     | N1                 | P0.00 / XL1      | Dedicated pin for NFC<br>Ezurio Devkit: Optional 32.768kHz crystal pad XL1 and<br>associated 7pF load capacitor inside nRF5340 chipset.                                                                                           |

| 35    | VDD_HV          | E1                 | VDD_HV           | 2.5V – 5.5V<br>See 3.6 BL5340 Power Supply Options                                                                                                                                                                                |

| 36    | D+              | B2                 | D+               | Ezurio Devkit: USB3                                                                                                                                                                                                               |

| 37    | P1.02 / I2C_SDA | AE1                | P1.02 / I2C_SDA  | Dedicated pins for High-speed TWI (1Mbps).                                                                                                                                                                                        |

| 38    | P1.03 / I2C_SCL | AF2                | P1.03 / I2C_SCL  | Ezurio Devkit: Multiple I2C sensors:- 3-axis<br>Accelerometer chip, LCD assembly, RTC chip,<br>Temp/Pres/HMD sensor chip, DAC chip, Eeprom chip,<br>Port Expander (PE) chip which has 4 LED's, 4 BUTTONS<br>connected to PE chip. |

| 39    | GND             | -                  | VSS              | -                                                                                                                                                                                                                                 |

| 40    | VBUS            | A5                 | VBUS             | 4.35V – 5.5V<br>See 3.6 BL5340 Power Supply Options                                                                                                                                                                               |

| 41    | P1.00           | M2                 | P1.00            | See Note 6                                                                                                                                                                                                                        |

| 42    | D-              | B4                 | D-               | Ezurio Devkit: USB3                                                                                                                                                                                                               |

| 42    | P1.01           | P2                 | P1.01            |                                                                                                                                                                                                                                   |

|       |                 | PZ                 | P1.01            | See Note 6                                                                                                                                                                                                                        |

| 44    | GND             | -                  | -                |                                                                                                                                                                                                                                   |

| 45    | P1.15           | B14                | P1.15            | Ezurio Devkit:                                                                                                                                                                                                                    |

| 46    | P0.05 / AIN1    | Y2                 | P0.05 / AIN1     | SD card DO/DAT0<br>Dedicated pin for ADC<br>Ezurio Devkit:<br>LCD assembly LCD_CTP_INT                                                                                                                                            |

| 47    | P1.13           | A17                | P1.13            | Ezurio Devkit:<br>SD card DI/CMD                                                                                                                                                                                                  |

| 48    | P1.14           | B16                | P1.14            | Ezurio Devkit:<br>SD card SCLK/CLK                                                                                                                                                                                                |

| 49    | P1.12           | B18                | P1.12            | Ezurio Devkit:<br>SD card CS_SD/DAT3                                                                                                                                                                                              |

| 50    | P1.11           | B20                | P1.11            | Ezurio Devkit: BOOT BUTTON (S4)                                                                                                                                                                                                   |

| 51    | P0.31           | B22                | P0.31            | See Note 6                                                                                                                                                                                                                        |

| 52    | P0.30           | B24                | P0.30            | See Note 6                                                                                                                                                                                                                        |

|       |                 |                    |                  | Dedicated pin for ADC                                                                                                                                                                                                             |

| 53    | P0.28 / AIN7    | AE31               | P0.28 / AIN7     | Ezurio Devkit: Ethernet chip SPI_SCK                                                                                                                                                                                              |

| 54    | nRESET          | AC31               | nRESET           | System Reset (Active Low). Internal 13K pull up inside nRF5340.                                                                                                                                                                   |

| 55    | SWDIO           | AA31               | SWDIO            | Pull up resistor (13K) inside nRF5340                                                                                                                                                                                             |

| 56    | SWDCLK          | W31                | SWDCLK           | Pull down resistor (13K) inside nRF5340                                                                                                                                                                                           |

| 57    | P1.10           | R31                | P1.10            | Ezurio Devkit: UART1_RX                                                                                                                                                                                                           |

| 58    | P0.29           | U31                | P0.29            | See Note 6                                                                                                                                                                                                                        |

| Pin # | Pin Name                      | nRF5340<br>QFN Pin | nRF5340 QFN Name      | Comment                                             |

|-------|-------------------------------|--------------------|-----------------------|-----------------------------------------------------|

| 59    | GND                           | -                  | VSS                   | -                                                   |

| 60    | P0.23                         | AK20               | P0.23                 | Ezurio Devkit:                                      |

| 00    | 1 0.20                        | A1120              | 1 0.23                | INT1_ACC interrupt from 3-axis accelerometer        |

| 61    | P0.18 / QSPI_CSN              | AK14               | P0.18 / QSPI_CSN      | Dedicated pin for QSPI                              |

| 01    | 10.107 001 _001               |                    | 10.107 001 _001       | Ezurio Devkit: QSPI flash chip                      |

| 62    | P0.14 / QSPI_101              | AK8                | P0.14 / QSPI_IO1      | Dedicated pin for QSPI                              |

| 02    |                               | AIXO               |                       | Ezurio Devkit: QSPI flash chip                      |

| 63    | P0.04 / AIN0                  | V2                 | P0.04 / AIN0          | Dedicated pin for ADC                               |

| 00    | 1 0.047 Alito                 | ٧Z                 | 1 0.047 Airto         | See Note 6                                          |

|       |                               |                    |                       | Dedicated pin for ADC                               |

| 64    | P0.06 / AIN2                  | AB2                | P0.06 / AIN2          | Ezurio Devkit:                                      |

|       |                               |                    |                       | LCD assembly LCD_Reset                              |

| 65    | P0.07 / AIN3 AD2 P0.07 / AIN3 |                    | Dedicated pin for ADC |                                                     |

| 05    | FU.U/ / AINJ                  | ADZ                | FU.U77 AINJ           | Ezurio Devkit: Interrupt from Ethernet chip INT_ETH |

| 66    | GND                           | -                  | VSS                   | -                                                   |

| 67    | GND                           | -                  | VSS                   | -                                                   |

| 68    | GND                           | -                  | VSS                   | -                                                   |

| 69    | GND                           | -                  | VSS                   | -                                                   |

| 70    | GND                           | -                  | VSS                   | -                                                   |

| 71    | GND                           | -                  | VSS                   | -                                                   |

|       | RF_pad                        |                    |                       | RF pad active on BL5340 RF pin variant 453-0053.    |

| 72    | or NC                         | -                  | -                     | NC on BL5340 Integrated antenna variant 453-0052    |

| 73    | GND                           | -                  | VSS                   | -                                                   |

| 74    | GND                           | -                  | VSS                   | -                                                   |

| 75    | GND                           | -                  | VSS                   | -                                                   |

# Pin Definition Notes:

| Note 1             | GPIO = General Input or Output (GPIO level voltage tracks VDD pin). AIN = Analog input.                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------|

| GPIO               | If GPIO is selected as an input, ensure the input is not floating (which can cause current consumption to       |

|                    | drive with time in low power modes (such as System ON Idle), by selecting the internal pull up or pull down.    |

|                    | Must connect all GND pads to host board PCB GND plane.                                                          |

| Note 2             | QSPI, High-Speed SPI (SPIM4) 32 Mbps, TWI 1 Mbps and Trace come on dedicated GPIO pins only. Other              |

| QSPI/SPI/TWI/Trace | lower speed SPI (16 Mbps, 8 Mbps, 4 Mbps, 2 Mbps, 1 Mbps, 500 kbps, 250 kbps, 125 kbps) and TWI (400            |

|                    | kbps, 250 kbps, 100 kbps) can come out on any GPIO pins.                                                        |

| Note 3             | If using the USB interface, then the BL5340 VBUS pin (pin40) must be connected to external supply within        |

| USB                | the range 4.35V to 5.5V. When using the BL5340 VBUS pin (pin40), you MUST externally fit a 4.7uF to             |

|                    | ground.                                                                                                         |

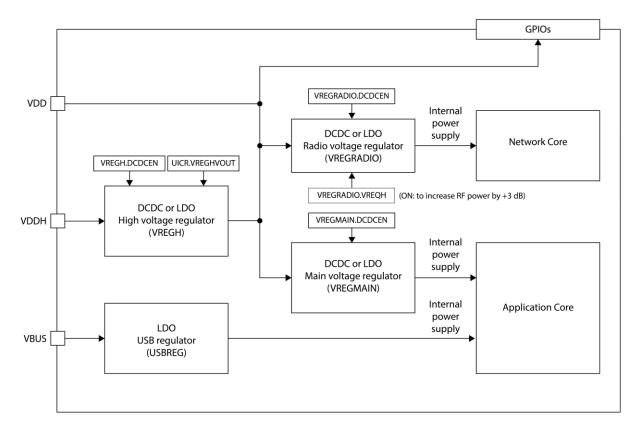

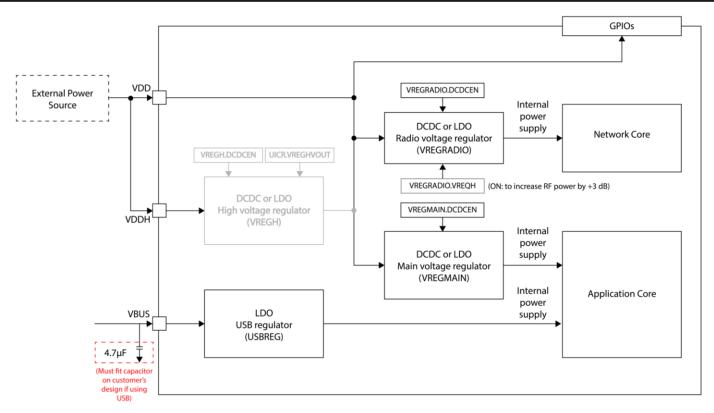

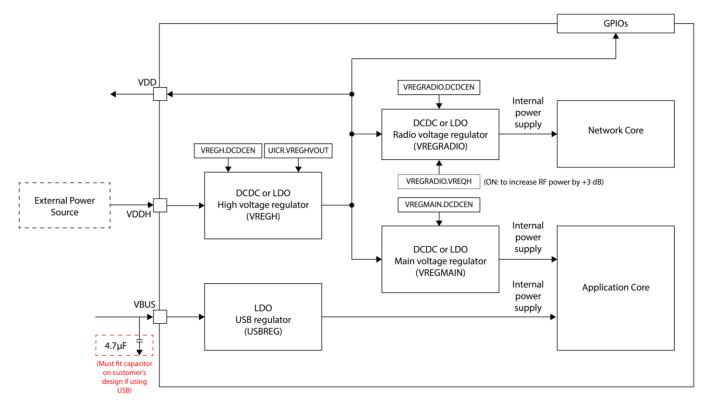

| Note 4             | Customer MUST bring out SWDIO, SWCLK, nRESET, VDD, GND for programming purposes.                                |